상태도 (오토마타 이론)

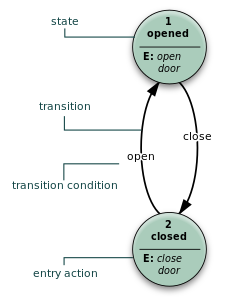

상태도(상태 다이어그램, 영어: State diagram)는 오토마타 이론(영어: Automata Theory) 또는 유한 상태 기계(영어: Finite-state machine, FSM)에서 상태와 상태천이를 표현하기 위해 도식화 해서 표현하는 그림을 말한다. 상태는 유한한 상태로 설정하고 추상화해야 한다. 도식 표현시 목적하는 상태를 추상화 한 다음, 상태변화에 대한 설정을 한다. 이때 상태 변화는 입력에 의해 이루어지고 어떤 상태로 존재하는가는 출력으로 나타낼 수 있다. 상태 유지는 외부 이벤트 없이도 계속 유지 되고, 변화는 주로 외부 입력에 의해 행해진다. 내부상태가 출력이 될 수도 있지만, 상태 변화시에도 출력을 만들 수 있다.

주로 컴퓨터 공학이나 논리회로 설계에서 많이 사용한다. 설계시, 설계 표현을 통해 복잡한 문제에서 나오는 오류를 줄일 수 있다.

프로그램에서도 프로그램 실행이 진행하는 과정상, 상태를 통해 개념화 한 다음 추상화 해서 그림을 그리고 코딩을 하면 오류를 줄이는 문서로써 유효하다. 예를 들어 윈도우형 계산기를 프로그램 할 때, 숫자버튼과 연산버튼등의 입력 절차를 결정할 때 숫자의 입력 상태와 연산 입력등을 상태도로 나타낼 수 있다.

논리회로에서 순차회로의 카운터 등의 응용회로에서 각각의 상태를 구분하고 입력에 따라 상태 변화를 도식화 할 수 있다. 문서화의 한 부분으로 설계를 쉽게 하도록 도와준다. FPGA의 설계시에도 복잡한 회로 표현에 유효하다. 경우에 따라 개발도구에서 상태도를 그리거나 VHDL 코드 생성을 돕는 도구도 있다.

상태도를 그리는 도구의 대표적인 것 중의 하나가 통합 모델링 언어(UML)의 많은 기능중에 상태도(state diagram)를 이용하면 된다. UML에서 하나의 부분으로 그리는 도구를 제공한다.

설계 시작부터 시작하여 오류검증 단계를 거쳐 최종목적물의 사용설명서까지 다양한 문서화 작업을 할 수 있고 기술표현에 많은 도움을 준다.